基于QUARTUSII图形输入电路的设计

一、 实验目的

1、通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。

2、初步了解QUARTUSII原理图输入设计的全过程。

3、掌握组合逻辑电路的静态测试方法。

二、 实验原理

3-8译码器三输入,八输出。当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。其真值表如表1-1所示

|

输入 |

输出 |

|

A |

B |

C |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

表1-1 三-八译码器真值表

译码器不需要像编码器那样用一个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。

三、 实验内容

在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED来表示三八译码器的八个输出(D0-D7)。通过输入不同的值来观察输入的结果与三八译码器的真值表(表1-1)是否一致。实验箱中的拨动开关当开关闭合(拨动开关的档位在下方)时其输出为低电平,反之输出高电平。

LED灯与其对应的端口为高电平时LED就会发光,反之LED灯灭。

四、 实验步骤

下面将通过这个实验,向读者介绍QUARTUSII的项目文件的生成、编译、管脚分配以及时序仿真等的操作过程。

1、建立工程文件

1)选择开始>程序>Altera>QuartusII10.0SP1> QuartusII10.0SP1,运行QUARTUSII软件。或者双击桌面上的QUARTUSII的图标运行QUARTUSII软件,出现如图1-3所示,如果是第一次打开QUARTUSII软件可能会有其它的提示信息,使用者可以根据自己的实际情况进行设定后进入图1-1所示界面。

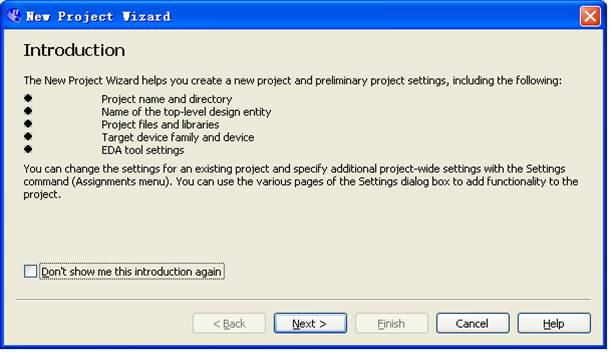

图1-2 新建工程对话框

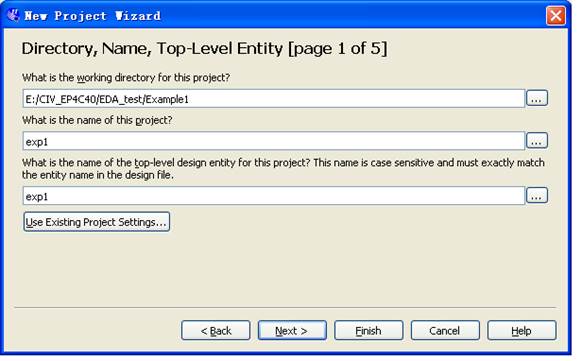

图1-3 指定工程名称及工作目录

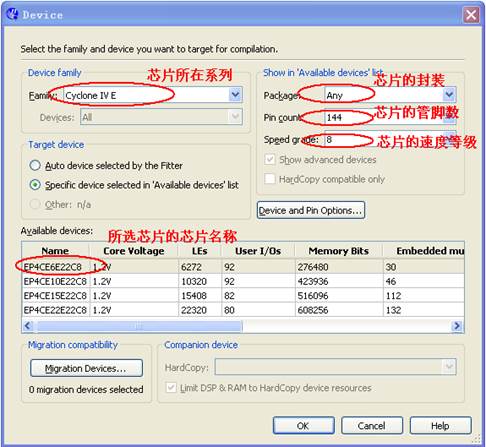

4)点击NEXT,进入下一个设定对话框,按默认选项直接点击NEXT进行器件选择对话框。如图1-4所示。这里我们以选用CycloneIV系列芯片EP4CE6E22C8N为例进行介绍。用户可以根据使用的不同芯片来进行设定。