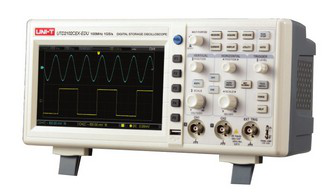

| 型号 | UTD2102CEX | |

| 通道数 | 2 | |

| 带宽 | 100MHz | |

| 最大采样率 | 1 GS/s | |

| 上升时间 | ≤3.5ns | |

| 存储深度 | 25kpts | |

| 波形捕获率 | ≥2,000wfms/s | |

| 垂直灵敏度 | 1mV/div ~ 20V/div | |

| 时基范围(s/div) | 2ns/div~50s/div | |

| 存储方式 | 设置、波形、位图 | |

| 触发 | ||

| 触发频率计 | 6位触发频率计 | |

| 触发类型 | 边沿、脉宽、交替 | |

| 触发电平范围 | 内部 | 距屏幕中心±5div |

| EXT | ±3V | |

| 释抑范围 | 80ns~1.5s | |

| 边沿触发 | ||

| 边沿类型 | 上升、下降、上升&下降 | |

| 脉宽触发 | ||

| 触发模式 | 正脉宽(大于,小于,等于),负脉宽(大于,小于,等于) | |

| 脉冲宽度范围 | 20ns~10s | |

| 交替触发 | ||

| CH1触发 | 边沿、脉宽 | |

| CH2触发 | 边沿、脉宽 | |

| 测量 | ||

| 光标 | 手动模式 | 光标间电压差(ΔV),光标间时间差(ΔT),ΔT的倒数(Hz)(1/ΔT) |

| 追踪模式 | 波形点的电压值和时间值 | |

| 自动测量模式 | 允许在自动测量时显示光标 | |

| 自动测量 | 峰峰值、幅值、最大值、最小值、顶端值、底端值、中间值、平均值、均方根值、周期平均值、周期均方根、过冲、预冲、频率、周期、上升时间、下降时间、正脉宽、负脉宽、正占空比、负占空比、上升延迟 、下降延迟 | |

| 数学操作 | 加、减、乘、除、反相 | |

| 存储波形 | 20组波形、20种设置 | |

| FFT | Window | Hanning、Hamming、Blackman、 Rectangular |

| 采样点 | 1024 points | |

| 李沙育 | 带宽 | 50MHz/70MHz/100MHz |

| 图形 | ||

| 相位差 | ±3 degrees | |

| 其它 | ||

| 接口功能 | 标配:USB OTG | |

| 一般参数 | ||

| 电源 | 100V~240VACrms,50Hz/60Hz | |

| LCD尺寸 | 7英寸TFT LCD ,WVGA(800×480) | |

| 机身颜色 | 象牙白+灰色 | |

| 机身重量 | 2.2 kg | |

| 机身尺寸(W×H×D) | 306mm×134mm×122mm | |

| 标准配件 | 探头×2(1:1,10:1可切换)、电源线、USB连接线、软件光盘 | |

| 标准包装 | 纸箱 | |

| 标准包装数量 | 2台 | |

| 标准包装尺寸 | 450mm× 420mm × 280mm | |

| 标准包装箱毛重 | 8.5 kg | |

| 可选配件 | LA模块:UT-M09 | |