八位七段数码管动态显示电路的设计

一、 实验目的

1、 了解数码管的工作原理。

2、 学习七段数码管显示译码器的设计。

3、学习VHDL的CASE语句及多层次设计方法。

二、 实验原理

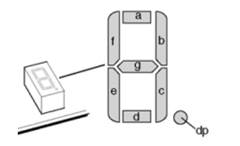

七段数码管是电子开发过程中常用的输出显示设备。在实验系统中使用的是两个四位一体、共阴极型七段数码管。其单个静态数码管如下图4-4-1所示。

图4-1 静态七段数码管

由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。反之则不亮。共阳极性的数码管与之相么。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

三、 实验内容

本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。在实验中时,数字时钟选择1024HZ作为扫描时钟,用四个拨动开关做为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

四、 实验步骤

1、 打开QUARTUSII软件,新建一个工程。

2、 建完工程之后,再新建一个VHDL File,打开VHDL编辑器对话框。

3、 按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序,用户可参照光盘中提供的示例程序。

4、 编写完VHDL程序后,保存起来。方法同实验一。

5、 对自己编写的VHDL程序进行编译并仿真,对程序的错误进行修改。

6、 编译仿真无误后,根据用户自己的要求进行管脚分配。分配完成后,再进行全编译一次,以使管脚分配生效。

7、 根据实验内容用实验导线将上面管脚分配的FPGA管脚与对应的模块连接起来。

如果是调用的本书提供的VHDL代码,则实验连线如下:

CLK:FPGA时钟信号,接数字时钟CLOCK3,并将这组时钟设为1464HZ。

KEY[3..0]:数码管显示输入信号,分别接拨动开关的K4,K3,K2,K1。

LEDAG[6..0]:数码管显示信号,接数码管的G、F、E、D、C、B、A。

SEL[2..0]:数码管的位选信号,接数码管的SEL2、SEL1、SEL0。

8、 用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。观察实验结果是否与自己的编程思想一致。

五、 实验现象与结果

以设计的参考示例为例,当设计文件加载到目标器件后,确认信号连接线已正确连接,将数字信号源模块的时钟选择为1464HZ,拨动四位拨动开关,使其为一个数值,则八个数码管均显示拨动开关所表示的十六进制的值。

六、 实验报告

1、 绘出仿真波形,并作说明。

2、 明扫描时钟是如何工作的,改变扫描时钟会有什么变化。

3、 实验原理、设计过程、编译仿真波形和分析结果、硬件测试结果记录下来。