вЛЁЂЯЕЭГзщГЩ

1ЁЂЕчдДЃК НЛСїЪфШыЃК220V±10% ЁЂ50Hz

ЙЬЖЈжБСїЪфЃКГі5V/2AЁЂ±12V/0.5A ЃЛ

2ЁЂЪжЖЏЕЅТіГхЕчТЗ2зщЃКУПзщПЩЭЌЪБЪфГіе§ИКСНИіТіГхЃЌТіГхЗљжЕЮЊTTLЕчЦНЁЃ

3ЁЂСЌајТіГхдДЃК0ЁЋ100KHzЁЃ

4ЁЂЙЬЖЈЦЕТЪТіГхдД4ТЗЃЌЪфГіЮЊTTLЕчЦНЃК1HzЁЂ8HzЁЂ32HzЁЂ1KHzЃЛ

5ЁЂЪБађТіГхЗЂЩњЕчТЗМАЦєЭЃПижЦЕчТЗЁЃПЩВњЩњЫФТЗТіГхаХКХЃЌТіГхжмЦкгыЪфШыЕФЪБжгаХКХЯрЭЌЃЌЫФИіТіГхжЎМфвРДЮЯрВю1ИіЪфШыЪБжгжмЦкЁЃ

6ЁЂ10ЮЛТпМЕчЦНЪфШыПЊЙиЃКПЩЪфШыЕЭЕчЦН‘0’ЁЂИпЕчЦН‘1’ЃЈЮЊе§ТпМЃЉЁЃ

7ЁЂ10ЮЛТпМЕчЦНжИЪОЕЦЃКжИЪОЕЦССБэЪОИпЕчЦН‘1’ЃЌжИЪОЕЦУ№БэЪОЕЭЕчЦН‘0’ЁЃ

8ЁЂЪ§ТыЙмЯдЪОЃКЫФЮЛгЩЦпЖЮLEDЪ§ТыЙмзщГЩЕФBCDТывыТыЯдЪОЕчТЗЃЌМА1ЮЛЦпЖЮLEDЪ§ТыЙмЁЃЙЉЪ§зжжгЁЂШеРњЕШЪЕбщЯдЪОгУЁЃ

9ЁЂбяЩљЦїМАЧ§ЖЏЕчТЗЁЃПЩгУзїЪБжгБЈЪБЁЂБЈОЏМАвєРжбнзрЕФЗЂЩљзАжУЁЃ

10ЁЂПЩБфЕчЮЛЦї3жЛЃЌзшжЕЗжБ№22KЃЌ50KЃЌ100KЁЃ

11ЁЂBCDАЮТыПЊЙи2зщ

12ЁЂТпМБЪ

13ЁЂЛљБОУХЕчТЗЪЕбщЧјЃКУцАхЩЯЛгаЕчТЗдРэЭМЁЃ

ЃЈ1ЃЉJKДЅЗЂЦї4зщ ЃЈ2ЃЉDДЅЗЂЦї4зщ ЃЈ3ЃЉгыУХ4зщ

ЃЈ4ЃЉЛђУХ4зщ ЃЈ5ЃЉгыЗЧУХ4зщ ЃЈ6ЃЉвьЛђУХ4зщ

ЃЈ7ЃЉЫФЪфШыгыЗЧУХ2зщ ЃЈ8ЃЉЗЧУХ6зщ ЃЈ9ЃЉNE555ЕчТЗ1зщ

14ЁЂПЊЗХЪЕбщЧјЃЌгУгкРЉеЙЪЕбщЁЂПЮГЬЩшМЦЪЙгУЁЃ

ЃЈ1ЃЉ20аОдВПзВхзљжЛЃЌ16аОдВПзВхзљ2жЛЃЌ14аОдВПзВхзљ2жЛЃЌ8аОдВПзВхзљ1жЛ

ЃЈ2ЃЉЗжСЂдЊМўНгВхЧјЃЌПЩНгВхЕчзшЁЂЕчШнЁЂЮШбЙЙмЁЂЖўМЋЙмЁЂШ§МЋЙмЕШдЊЦїМўЃЌЗНБуРЉеЙЁЃ

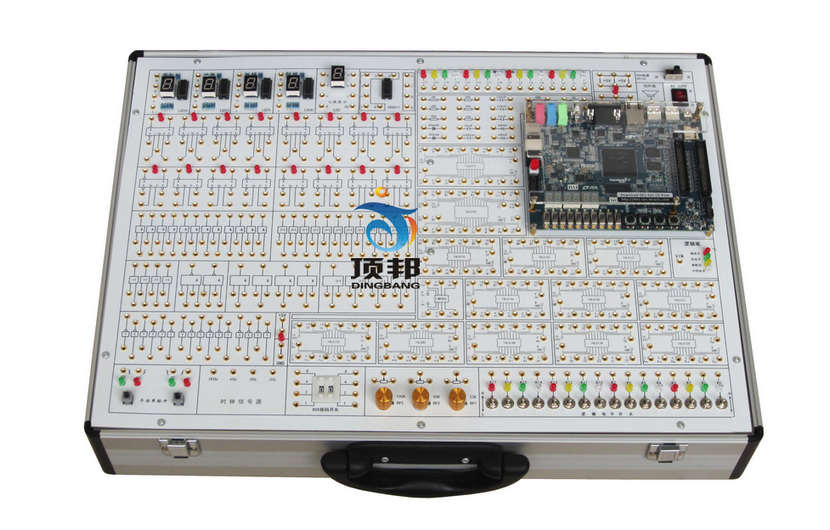

15ЁЂEDAЪЕбщЕЅдЊЃЌВЩгУДѓШнСПЕФAltera FPGAаОЦЌEP5CSEMA5зїЮЊКЫаФАхЁЃ

16ЁЂEP5CSEMA5КЫаФАхзЪдДЃК

ЃЈ1ЃЉ FPGAКЫаФЦїМўЃКCyclone V SoC 5CSEMA5F31C6 DeviceЃЌ85KПЩБрГЬТпМзЪдДLEs, ФкЧЖ4450KИіДцДЂЦїФЃПщЃЌ6 ИіИпадФмЗжЪ§ЗжЦЕFractional PLLs, 2ИігВКЫФкДцПижЦЦїЃЛ

ЃЈ2ЃЉжЇГж64MB (32Mx16)SDRAMПижЦЦїЃЛ

ЃЈ3ЃЉжЇГжЖрЖЫПк1GB (2x256Mx16)DDR3 SDRAMПижЦЦїЃЈИпДя533 MHZЕФDDR3 ЁЂМЏГЩECCжЇГжЃЉЃЛ

ЃЈ4ЃЉЛљгкARMЕФгВКЫДІРэЦїЯЕЭГ(HPS)ЃКФкжУ800 MHz, ЫЋКЫARMCortex™-A9 MPCore™ ДІРэЦїЃЛ512-KBЙВЯэL2ИпЫйЛКДцЃЛ64 KBЕФScratchЦЌФкRAMЃЛ

ЃЈ5ЃЉЧЖШыЪНUSB-Blaster II (JTAG)ХфжУЕчТЗКЭЕчРТЃЈЭЈгУBаЭUSBНгПкЃЉЃЛжЇГжEPCS128ЩСДц(PFL)ХфжУЃЛ

ЃЈ6ЃЉСНИі USB 2.0 Host НгПкЃЛвЛИіUSBзЊUART НгПкЃЛжЇГж10/100/1000 ЧЇезвдЬЋЭјНгПкЃЛДјгаPS/2 ЪѓБъ/МќХЬНгПкЃЛДјгаIR ЪеЗЂЦї

ЃЈ7ЃЉХфБИСНИі40-pinРЉеЙНгПкЃЛвЛИі10-pin ADCЪфШыЃЛвЛИі LTC СДНгЦї(жЇГж(SPI) жїПиЦї,I2C авщДЋЪфКЭЭЈгУIOpin )ЃЛ4 ИігУЛЇздЖЈвхАДХЅ (FPGA x4)ЃЛ10 ИігУЛЇздЖЈвхПЊЙи(FPGA x10)ЃЛ11 гУЛЇздЖЈвхLEDs (FPGA x10 ; HPS x 1)ЃЛ2ИігВКЫДІРэЦїЯЕЭГАДХЅЃЛ6ИіЦпЖЮЪ§ТыЙмЃЛ

ЃЈ8ЃЉ24-bit VGAЯдЪОЪфГіЃЛ

ЃЈ9ЃЉвєЦЕВПЗжЃКжЇГж24-bit вєЦЕБрТыЃЌДјгаline inЁЂoutЁЂmicrophoneЪфШыНгПкЃЛ

ЃЈ10ЃЉгВКЫДІРэЦїЯЕЭГДјгаШ§жсМгЫйЖШДЋИаЦї

ЃЈ11ЃЉ12V DCЪфШы

ЖўЁЂЪЕбщЯюФП

ЃЈвЛЃЉЪ§зжЕчТЗЪЕбщ

1ЁЂУХЕчТЗЕФТпМЙІФмМАВтЪдЪЕбщ

2ЁЂзщКЯТпМЕчТЗЃЈАыМгЦїЁЂШЋМгЦїМАТпМдЫЫуЃЉЪЕбщ

3ЁЂДЅЗЂЦїЪЕбщЃЈвЛЃЉ R-SЁЂDЁЂJK

4ЁЂДЅЗЂЦїЪЕбщЃЈЖўЃЉ Ш§ЬЌЪфГіДЅЗЂЦїЁЂЫјДцЦї

5ЁЂЪБађЕчТЗВтЪдгыбаОП

6ЁЂМЏГЩМЦЪ§ЦїМАМФДцЦїЪЕбщ

7ЁЂвыТыЦїКЭЪ§ОнбЁдёЦїЪЕбщ

8ЁЂВЈаЮВњЩњЦїМАЕЅЮШЬЌДЅЗЂЦїЪЕбщ

9ЁЂ555ЪБЛљЕчТЗЪЕбщ

ПЩбЁзіШчЯТЪЕбщ

10ЁЂОЇЬхЙмПЊЙиЬиадЁЂЯоЗљЦїгыЧЏЮЛЦїЪЕбщ

11ЁЂTTLУХЕчТЗВЮЪ§ВтЪдЪЕбщ

12ЁЂCMOSУХЕчТЗВтЪдЪЕбщ

13ЁЂA/DЁЂD/AзЊЛЛЕчТЗЪЕбщ

14ЁЂЪБађЕчТЗгІгУЪЕбщ

15ЁЂЫФТЗгХЯШХаОіЕчТЗЪЕбщ

16ЁЂжЧСІОЙШќЧРД№ЦїЪЕбщ

17ЁЂЕчзгУыБэЪЕбщ

18ЁЂ3ЮЛАыжБСїЪ§зжЕчбЙБэЪЕбщ

19ЁЂЪ§зжЦЕТЪМЦЪЕбщ

20ЁЂАЮКггЮЯЗЛњЪЕбщ

21ЁЂЫцЛњДцДЂЦїМАЦфгІгУЪЕбщ

22ЁЂ8ТЗЧРД№ЦїЕчТЗЩшМЦЪЕбщ

23ЁЂЪ§зжжгЕчТЗЕФЩшМЦЪЕбщ

24ЁЂНЛЭЈЕЦПижЦТпМЕчТЗЩшМЦЪЕбщ

25ЁЂЦћГЕЮВЕЦПижЦЕчТЗ

26ЁЂРКЧђОКШќ30SМЦЪБЦї

ЃЈЖўЃЉEDAЦїМўПЊЗЂЩшМЦЪЕбщ

1ЁЂ ЕЅдЊЕчТЗЩшМЦЪЕбщЃК

ЪЕбщ1.1 зщКЯТпМ3-8выТыЦїЕФЩшМЦ

ЪЕбщ1.2 АыМгЦї

ЪЕбщ1.3 ШЋМгЦї

ЪЕбщ1.4 ШЋМѕЦї

ЪЕбщ1.5 4ЮЛЯђСПМгЗЈ/МѕЗЈЦї

ЪЕбщ1.6 ЯђСПГЫЗЈЦї

ЪЕбщ1.7 Ъ§ОнБШНЯЦї

ЪЕбщ1.8 ЖрТЗЪ§ОнбЁдёЦї

ЪЕбщ1.9 БрТыЦї

ЪЕбщ1.10 выТыЦї

ЪЕбщ1.11 ЖўНјжЦТызЊЛЛГЩBCDТы

ЪЕбщ1.12 BCDТызЊЛЛГЩЖўНјжЦТы

ЪЕбщ1.13 BCDТызЊЛЛГЩИёРзТы

ЪЕбщ1.14 зщКЯТпМЕчТЗЕФЩшМЦ

ЪЕбщ1.15 МђЕЅзДЬЌЛњ

ЪЕбщ1.16 ДЎШы/ВЂГівЦЮЛМФДцЦї

ЪЕбщ1.17 ВЂШы/ДЎГівЦЮЛМФДцЦї

ЪЕбщ1.18 ЖрЙІФмМФДцЦї

ЪЕбщ1.19 ЕЅТіГхЗЂЩњЦї

ЪЕбщ1.20 НкХФТіГхЗЂЩњЦї

ЪЕбщ1.21 ЦцХММьбщ

ЪЕбщ1.22 МЦЪ§Цї

ЪЕбщ1.23 7ЖЮЪ§ТыЙмЯдЪО

ЪЕбщ1.24 Ъ§зжжг

ЪЕбщ1.25 УыБэЩшМЦЪЕбщ

ЪЕбщ1.26 VGAНгПкЧ§ЖЏЪЕбщ

2ЁЂ NiosШэКЫЪЕбщЃК ЁЁ

ЪЕбщ2.1 NiosШэКЫЕФЩшМЦ

ЪЕбщ2.2 ЭтЩшФЃПщЕФЩшМЦ

ЪЕбщ2.3 QsysгІгУЯЕЭГЕФЩњГЩ

ЪЕбщ2.4 Nios IIШэКЫбщжЄвдМАNios II IDEШэМўЕФНщЩм

ЪЕбщ2.5 QsysЯЕЭГЕФPIOбщжЄ

ЪЕбщ2.6 7ЖЮЪ§ТыЙмЯдЪОЪЕбщ

ЪЕбщ2.7 АДМќМАВІТыПЊЙиЪЕбщ

ЪЕбщ2.8 LTC2308 ADзЊЛЛЪЕбщ

ЪЕбщ2.9 ЛљгкQSYSЕФuC/OS-IIВйзїЯЕЭГгІгУЪЕбщ

Ш§ЁЂЪЕбщЪвХфжУЗНАИ

ЪЕбщЪвУПШЫУПЬзХфжУЗНАИ(ЖўШЫЮЊвЛзщЃЌвЛзщгУвЛеХЪЕбщзР)

1ЁЂDB-SD11 БиХф 1ЬЈЁЃ

2ЁЂЪОВЈЦї здХф 1/2ЬЈЁЃ

3ЁЂЭђгУБэ здХф 1жЛЁЃ

4ЁЂЪЕбщзР здХф 1/2еХЁЃ

5ЁЂЪЕбщвЮ здХф 1 еХЁЃ